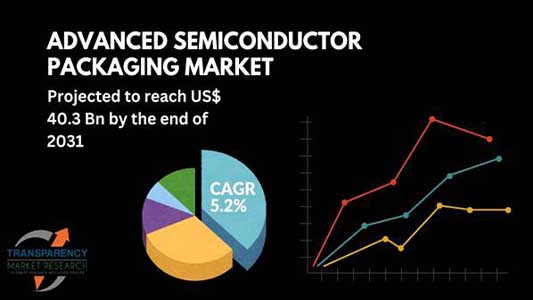

The global Advanced Semiconductor Packaging Market was valued at US$ 30.1 billion in 2022 and is projected to grow at a CAGR of 5.2% from 2023 to 2031, reaching an estimated US$ 40.3 billion by the end of 2031. Semiconductor packaging has emerged as a key enabler of the revolutionary technological improvements being driven by the semiconductor industry’s unrelenting pace of invention. Advanced semiconductor packaging has developed into an intricate field that affects device performance, efficiency, and form factor, and it is no longer just a protective shell for microchips. Advanced semiconductor packaging is ramping up to meet the demands of technologies like artificial intelligence (AI), 5G, the Internet of Things (IoT), and driverless vehicles, which call for electronics that are more potent and compact. The technologies, developments, and prospects influencing semiconductor packaging in the future are examined in this article.

The Role of Semiconductor Packaging

Semiconductor packaging is the final step in semiconductor fabrication, where the silicon chip is enclosed in a protective casing to prevent physical damage and environmental contamination. Beyond its traditional protective role, packaging now serves as a conduit for electrical connections and thermal management. Advanced packaging techniques ensure optimal performance and enable chips to work together seamlessly in complex systems.

In today’s interconnected world, advanced packaging plays a pivotal role in enhancing device performance, reducing power consumption, and supporting high-speed data transmission. It is particularly critical for applications requiring compact and lightweight designs, such as wearable devices and edge computing systems.

Key Technologies in Advanced Semiconductor Packaging

The evolution of semiconductor packaging has given rise to several advanced technologies, including:

System-in-Package (SiP)

System-in-Package (SiP) integrates multiple integrated circuits (ICs) and passive components into a single package. This approach enables the combination of different functionalities, such as processing, memory, and communication, within a compact footprint. SiP is widely used in smartphones, IoT devices, and wearable technology, where space constraints and multifunctionality are critical.

2.5D and 3D Packaging

2.5D packaging utilizes an interposer to connect multiple dies side by side, while 3D packaging stacks dies vertically. These architectures improve performance by reducing signal delay, power consumption, and interconnect length. 3D packaging, in particular, is gaining traction in applications like high-performance computing (HPC), AI accelerators, and data centers.

Fan-Out Wafer-Level Packaging (FOWLP)

FOWLP extends the silicon die beyond its original boundaries, enabling higher I/O density and better thermal performance. This technology eliminates the need for a substrate, reducing package size and cost while enhancing performance. FOWLP is particularly popular in mobile and automotive applications.

Chiplet-Based Design

Chiplet architecture breaks down a monolithic IC into smaller functional blocks, or chiplets, which are then interconnected within the package. This approach allows for greater design flexibility, faster time-to-market, and reduced development costs. Chiplets are increasingly used in HPC and AI processors to achieve modular scalability.

Through-Silicon Via (TSV)

Through-Silicon Via (TSV) technology creates vertical electrical connections through the silicon die, enabling high-speed data transfer between stacked dies. TSV is instrumental in enabling 3D ICs and high-bandwidth memory (HBM) solutions, which are critical for AI, machine learning, and gaming applications.

Heterogeneous Integration

Heterogeneous integration combines different types of ICs, including analog, digital, RF, and photonics, into a single package. This integration allows manufacturers to leverage the strengths of various materials and technologies, optimizing performance and efficiency. Heterogeneous integration is central to advancing 5G, IoT, and edge computing.

Trends Driving the Semiconductor Packaging Market

The semiconductor packaging market is being shaped by several key trends, including:

Increasing Demand for AI and Machine Learning

AI and machine learning applications require enormous computational power and data throughput. Advanced packaging techniques, such as 3D ICs and high-bandwidth memory, are critical to meeting these demands. Packaging innovations enable faster processing and energy efficiency, driving advancements in AI chips.

Proliferation of 5G Technology

The rollout of 5G networks demands compact, high-performance devices capable of handling massive data volumes at high speeds. Advanced packaging solutions, such as fan-out and heterogeneous integration, are enabling the development of 5G-compatible chips that deliver superior performance and reliability.

Growth of IoT Ecosystems

IoT devices require compact, energy-efficient, and cost-effective solutions. System-in-Package (SiP) and wafer-level packaging (WLP) technologies are driving the miniaturization and multifunctionality needed for IoT sensors, smart wearables, and connected home devices.

Sustainability and Energy Efficiency

The semiconductor industry is under increasing pressure to adopt sustainable practices. Advanced packaging technologies can improve energy efficiency by reducing power consumption and enhancing thermal management. Furthermore, substrate-free packaging methods like FOWLP contribute to material savings and reduced environmental impact.

Automotive Electronics and Autonomous Vehicles

The automotive industry’s transition to electric and autonomous vehicles is spurring demand for advanced semiconductor packaging. Robust, high-performance, and reliable packaging solutions are essential for automotive ICs, which must withstand extreme environmental conditions and provide seamless operation for safety-critical systems.

Challenges in Advanced Semiconductor Packaging

Despite its transformative potential, advanced semiconductor packaging faces several challenges:

- Cost and Complexity: Advanced packaging processes, such as 3D stacking and TSV integration, are complex and expensive, requiring significant capital investment and expertise.

- Thermal Management: As chips become denser and more powerful, managing heat dissipation is a critical challenge. Effective thermal solutions are essential to ensure performance and reliability.

- Supply Chain Constraints: The semiconductor supply chain is highly intricate, and disruptions can impact packaging material availability and manufacturing timelines.

- Testing and Reliability: Advanced packaging introduces new challenges in testing and reliability, particularly for heterogeneous and 3D integrated systems.

Future Opportunities in Semiconductor Packaging

The future of semiconductor packaging is brimming with opportunities. Emerging technologies and applications will continue to push the boundaries of what packaging can achieve:

- Quantum Computing: Advanced packaging will play a pivotal role in enabling the scalability and reliability of quantum processors, which require unique materials and designs.

- Neuromorphic Computing: Packaging solutions for neuromorphic chips will focus on reducing power consumption and improving connectivity to mimic human brain functionality.

- Flexible and Wearable Electronics: Innovative packaging technologies will drive the development of flexible, stretchable, and biocompatible electronics for healthcare and fitness applications.

- Photonics Integration: The integration of photonics with electronics will enable faster data transfer and improved energy efficiency, supporting applications like data centers and optical communications.